ISSN 2454-8065 International Journal of Applied Theoretical Science and Technology **volume 03, Issue 08, pp575-578, 30<sup>th</sup>** October 2016

# An Adaptive filter design based on Residue number system

Pamula srinu Assistant Professor ECE.

Siddhartha institute of technology & sciences. Hyderabad.

Abstract: Computerized channels are imperative things in Very Large Scale Integration (VLSI) outlines. The accessible Finite Impulse Response (FIR) channel prepares a long

transient reaction which considers as its significant impediment. To get over this disadvantage, Residue Number System (RNS) based FIR channels is been proposed which is clarifies in this paper. Rapid is acquired by utilizing the buildup math way that permits the calculation for channel yield by utilizing N FIR sub channels for diminished element extend working in parallel frame. Add up to three moduli 2n-

1, 2n, 2n+1 sets are utilized as a part of proposed RNS based Filter. 4-tap Low Pass Filter (LPF) sort for FIR channel and RNS based FIR channel alongside 4-tap LPF are planned. Verilog HDL dialect is utilized for RTL section and broke down in this paper. The reenactment is done utilizing Xilinx **EDA apparatus Integrated Simulation Environment ISE-12.2**

Keywords: ISE, RNS, Verilog, LPF, FIR, EDA, DSP, moduli, RTL.

## **I-Introduction**

As of late, there has been critical improvement in the field for Digital Signal Processing (DSP) alongside the headway in VLSI innovation. Different applications for DSP incorporates sound, picture and video handling and shopper gadgets [1]. FIR advanced channels are broadly utilized as a part of computerized flag preparing by goodness for soundness and simple usage. The significant downside for FIR channels is the expanded sum for computation expected to prepare a flag through the FIR channel. The approach for VLSI innovation and DSP processors gives a chance to fundamentally expanded productivity for RNS to limit the deferral. RNS methodologies are getting to be distinctly popular for planning high proficient DSP processors in light of its capacity to have convey free number juggling calculation. The convey free calculations prompt to singular amount execution of math operation on its buildups. in any case, in RNS, determination of moduli is one for the most critical perspective that decides bit range, control utilization, productivity, speed and so forth. In RNS, number juggling operations on huge whole numbers are finished by part them into littler buildups and playing out the operations autonomously and parallel shape, in this manner accelerating the entire operation alluded in paper [2, 3]. In proposed paper, an attempt has been made to plan and mimic LPF sort for RNS based FIR channels with the thought for 4 tap utilizing Verilog.

## II. FIR Filter

The yield say (y) for any LTI framework is controlled by portrayed by the accompanying condition, which

x(n) is information flag

performing convolution its info flag say (x) with its drive reaction say (b). For a discrete time FIR channel, the yield is weighted whole for the present and some limited number for past qualities for the information. The working is demonstrates the yield succession y[n] in wording for its information grouping x[n]

> $()\Sigma$  $_{i}x(n-i)....(1)$

Here

y(n) is yield flag

bi are the coefficients of channel, additionally called as tap weights, that builds up the drive reaction and N is the request of channel. A Nth-arrange channel has appeared on the right-hand side in condition (1). The x(n-i) in these terms are alluded to as taps, premise on the structure for a tapped defer line there are numerous executions or pieces gives the postponed contributions to the augmentation calculations.

FIR computerized channels have precisely direct stage reaction and experience the ill effects of the impacts for limited word length as contrasted and IIR advanced channels. The fundamental segments for FIR channel are viper, multiplier and postponement. The convey engendering postponement is a constraining element for the snake and multiplier. The deferral for FIR channels is lessened by joining RNS based modulo snake and modulo multiplier in the basic FIR channel. Prior to the recreation for FIR channel, the coefficients are scaled by the accompanying principles given beneath.

## III- RNS based FIR filter

Specialists have examined about the streamlined RNS based FIR channel display [4, 5]. It is characterized by a set for generally prime whole numbers called the moduli. The moduli set are indicated as {m1,m2,.....mn}where m1,m2,.....mn is the modulus. Every whole number can be spoken to as a set for littler numbers called the buildups. The buildup set is indicated

rn}where ri is ith the deposit. The deposit is {r1,r2, characterized as the slightest positive leftover portion when X is separated by the moduli mi[5]. This connection can be notationally composed in light of the compatibility and the condition is given beneath

$Mod m_{i} = r_{i} \qquad (2)$

The same congruence can be written in an alternative notation as:

$= r_i$ ....(3)

The RNS is capable for uniquely representing all integers X that lie in its dynamic range. The dynamic range is determined by the moduli-set {m1,m2,...,mn} and denoted as M where:

....(4)

SSN 2454-8065 International Journal of Applied Theoretical Science and Technology volume 03, Issue 08, pp575-578, 30th October 2016

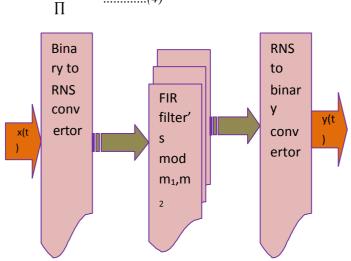

Figure 1: RNS based FIR filter

The RNS gives one of a kind representation to all numbers in the range in the vicinity of 0 and M-1. On the off chance that the whole number X is more noteworthy than M-1, the RNS representation rehashes itself. Accordingly, more than one number may have a similar deposit representation. Emphasize that the moduli must be generally prime to have the capacity to misuse the full element go M. The underneath figure 1 demonstrates the general structure for RNS based FIR channel. X(t) and Y(t) are the info and yield for this figure. The forward and switch transformation depends on the exceptional moduli set and the New Chinese Remainder Theorem (NCRT) and the three FIR channel squares are utilized here to accelerate the procedures.

**Decision for Moduli:** The decision for moduli ought to fulfill the accompanying conditions. They ought to be generally prime. The moduli ought to be as little as conceivable so that operations modulo require least computational time. The moduli ought to infer straightforward weighted to RNS and RNS to weighted transformations and additionally basic RNS number juggling. The moduli set ought to be for the structures 2k+1,2k-1 and 2k for basic changes and basic math in RNS framework. The item for the moduli ought to be sufficiently huge with a specific end goal to actualize the coveted element extend. The moduli ought to make an adjusted disintegration for the dynamic range.

## IV-DESIGN METHODOLOGY

Proposed work demonstrates another approach for forward change. In forward transformation stage is for principal significance as it is considered as an overhead in the general RNS. Forward converters are typically ordered into two classifications in view of the moduli utilized. The main classification incorporates forward converters in view of discretionary moduli-sets. These converters are normally developed utilizing look tables. The second classification incorporates forward converters in view of extraordinary moduli-sets. The utilization for unique moduli-sets disentangles the forward transformation calculations and models alluded in[6]

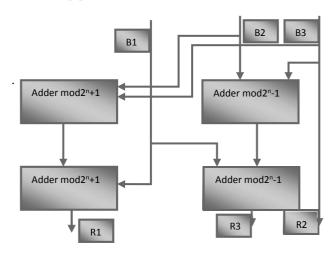

Normally, the extraordinary moduli-sets are alluded to as minimal effort moduli-sets. In this segment, exceptional moduli-set {2n+1,2n,2n-1}is engaged as it is the most usually utilized moduli-set utilized for this outline. Analysts have examined about the significance for exceptional moduli-put forth converters. A normal engineering for the execution for a forward converter from twofold to RNS representation utilizing the exceptional moduli-set is appeared in Figure 2. One path for actualizing a deposit viper for modulo m structure is formed for one n-bit snake alluded in [7]

Figure 2: Forward {2<sup>n</sup>+1, 2<sup>n</sup>, 2<sup>n</sup>-1} Converter

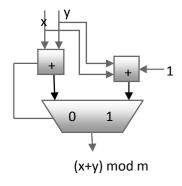

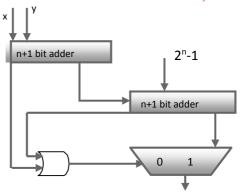

The modulo 2n-1 snake structure is appeared in figure 3. This viper includes two n-bit numbers, X and Y in the initial step. In the second step, the outcome is given to the multiplexer for 2n-1 snake. In 2n+1adder, the principal stage is same as that for 2n-1 viper yet the second step is finished with the two's supplement for modulo m. The last outcome is chosen between the two yields as per the two yield conveys. Modulo 2n+1 snake in arrangement strategy is appeared in Figure 4 The postponement for modulo 2n+1 structure is equivalent to the deferral for two (n+1)- bit adders and also the postponement for one (n+1)- bit 2×1multiplexer alluded in [8].

Figure 3: modulo 2<sup>n</sup>-1 adder

**N 2454-8065** International Journal of Applied Theoretical Science and Technology volume 03, Issue 08, pp575-578, 30<sup>th</sup> October 2016

Figure 4: modulo 2n+1 adder

## V- Tool, platform and language

Dialect and instruments utilized as a part of this proposition work. Xilinx ISE 12.2 is utilized for reenactment and Verilog has been considered as a programming dialect

Verilog is the Hardware Description Language that might be utilized to outline a computerized framework at many levels for reflection, going from the algorithmic level to the base door level.

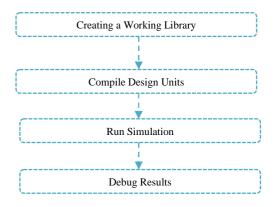

The Xilinx ISE Simulator (ISim) is a HDL test system that empowers you to perform utilitarian (behavioral) and timing reenactments for VHDL, Verilog and blended dialect outlines. The fundamental reproduction stream is appeared in the figure 5

Figure 5: Simulation Flow

The target device used is Xilinx's Vertex 4 xc4vlx25-12ff668.

Figure 6: Package marking for target device

#### VI- Conclusion

FIR Filter in Morden advanced and discrete information correspondence plays exceptionally significance roll. Leaving works are itself an accomplishment yet with long calculation time proposed work simply give another way to deal with supplant that very perplexing calculation with straightforward deposit based calculations. Paper work for the most part proposed another forward  $\{2n+1, 2n, 2n-1\}$ convertor which utilizes modulo 2n+1 and 2n-1 snake and that forward convertor will further be utilized as a part of the plan for FIR channel and RNS based FIR channel considering 8-tap LPF by utilizing Verilog dialect. The forward (double to RNS) and switch (RNS to parallel) change hinders for RNS based FIR channels have been intended for {2n+1,2n,2n-1} moduli and afterward joined in the RNS based FIR channel which is recreated and broke down.

## REFERENCES

- [1] Richard Conway, John Nelson, "Enhanced RNS FIR channel Architecture", IEEE Transaction on Circuits and Systems, vol.51, no.1, pp.26-28, January 2004.

- [2] Salvatore Pontraelli, Gian Carlo Cardarilli, Marco Re, Adelio Salsano, "Improved usage for RNS FIR channels in view of FPGAs", Springer Journal Signal Processing System, vol. 67, no.3, pp.201-212, September 2012.

- [3] Pemmaraju V. Ananda Mohan, "RNS to Binary converter for a Three moduli set {2n+1-1,2n, 2n-1}", IEEE Transaction on Circuits and Systems, vol.54, no.9, pp.775-779, September 2007.

- [4] E. Grosswald, "Subjects from the hypothesis for Numbers", Collier Macmillan Ltd., New York, 1996.

- [5] A. Omondi and B. Premkumar, "Buildup Number System: Theory and usage", Imperial College Press, 2007, (ISBN 978-1-86094-866-4).

- [6] Jean-Luc Beuchat, "Some Modular Adder and Multipliers for Field Programmable Gate Arrays", Proceedings for the IEEE seventeenth International Symposium on Parallel and Distributed Processing, Washington DC, USA, pp-190.2, April 2003.

- [7] Somayeh Timarchi, Keivan Navi, "Enhanced Modulo 2n +1 Adder Design", World Academy for Science, Engineering and Technology, 2001.

- [8] George Ignatius ,Murali Krishna Varma U, Nitish. S. Krishna,Sachin. P.V. P. Sudheesh, Extended Kalman Filter based Estimation for Fast Fading MIMO Channels, IEEE, 2013